# **RESEARCH PAPER**

# Performance Improvement of Double Gate Nano-TFET Via Combination of Dual Material Gate-Drain Overlap and Source Pocket

Mina Mazrouei 1, Daryoosh Dideban 1,2\*, Mohammad Karbalaei 1

- <sup>1</sup> Institute of nanoscience and nanotechnology, University of Kashan, Kashan, Iran

- <sup>2</sup> Department of Electrical and Computer Engineering, University of Kashan, Iran

#### ARTICLE INFO

#### Article History:

Received 13 April 2025 Accepted 26 June 2025 Published 01 July 2025

#### Keywords:

Ambipolar conduction Dual metal gate Source pocket TFET

#### **ABSTRACT**

Although tunneling field effect transistors (TFETs) exhibit low threshold swing and enable good scalability, but TFETs suffer from two main problems: low ON-state current ( $I_{ON}$ ) and intrinsic ambipolar conduction. In this work, we propose a structure of double-gate TFET with 50nm channel length, which has lower ambipolar conduction and higher ONstate current compared to conventional double-gate TFET. In the proposed TEFT, in order to achieve the minimum ambipolar conduction, dual material gate (DMG) has been integrated with the gate-drain overlap (GDO), and in order to simultaneously improve the ambipolar conduction and the ON-state current, the source pocket (SP) has been added to the structure. We show in proposed device, by increasing the length and thickness of the source pocket, the ON-state current increases. In addition, increasing doping of the source pocket shows enhanced ION order up to 4E-3. We compare 4 TFET structures, namely DG-TFET, DMG-DGTFET, GDO-DMG-DGTFET, and the proposed structure (SP-GDO-DMG-DGTFET). We show that the proposed structure has a higher  $I_{ON}/I_{OFF}$  ratio (1E14) and less ambipolar conduction than other structures under study and is more suitable for digital applications. Also, by calculating transconductance  $(g_{\scriptscriptstyle m}),$  gate-drain capacitance  $(C_{\scriptscriptstyle gd}),$  gate-source capacitance  $(C_{\scriptscriptstyle gs}),$  we show that the proposed structure has the highest cut off frequency (0.6THz) compared to other structures under study and is more suitable for high frequency applications.

### How to cite this article

Mazrouei M., Dideban D., Karbalaei M. Performance Improvement of Double Gate Nano-TFET Via Combination of Dual Material Gate-Drain Overlap and Source Pocket. J Nanostruct, 2025; 15(3):1406-1415. DOI: 10.22052/JNS.2025.03.055

#### INTRODUCTION

One of the major problems to continue the scaling process of the CMOS devices is the power consumption. Scaling of transistors and increasing the density of transistors on the chip increases the power density on the chip. Therefore, according to the scaling of the transistors, the supply voltage should be reduced. Although scaling the supply

voltage reduces dynamic power consumption, but to achieve the same ON-current, the threshold voltage must be scaled as the supply voltage decreases. Decreasing the threshold voltage leads to an exponential increase of OFF-state current and the static power. The exponential increase of OFF-state current is due to threshold swing limit of 60 mV/decade, which is caused by the thermal carrier

<sup>\*</sup> Corresponding Author Email: dideban@kashanu.ac.ir

injection mechanism [1]. The carrier transmission mechanism in TFETs (tunneling field effect transistors) is based on band-to-band tunneling (BTBT), so they have low subthreshold swing compared to MOSFET and are the most promising devices for low-power applications [2-3-4-5-6]. Although TFETs can overcome the theoretical limit of subthreshold swing of conventional MOSFETs and can be used in ultra-low voltage circuits that are very energy efficient, but they face two major problems: low ON-state current and ambipolar conduction.

The tunneling probability of the carriers is reduced due to the large tunneling resistance in the TFET. As a result, the ON-state current of TFET is significantly lower than of the MOSFET [7-8]. To enhance the ON-state current of TFET, some researches have been done, for example: using III-V compound semiconductor [9-10-11], using high-k gate oxide (HfO2) [12-13], increasing the tunnel area [14], using dual source region [15], increasing the source doping concentration [16]. Also, an abrupt source doping profile increases  $I_{_{

m ON}}$  [17]. In addition, the ON-state current of the double-gate TFET is greatly improved compared to the conventional single-gate TFET [18-19]. This is due to the high dependence of the barrier width on the gate voltage, and consequently the width of the barrier can be better controlled by using double gates in the TFET.

Another disadvantage in TFETs is the presence of ambipolar conduction. Ambipolarity is an intrinsic phenomenon of TFET technology where the conduction occurs for both positive and negative gate voltages. The ambipolar current (I<sub>amb</sub>) flows due to BTBT at the channel-drain junction for negative gate voltage for n-type TFET, and positive for p-type, which makes TFET technology unsuitable for complementary logic digital systems [20]. Fig. 2 shows the schematic representation of inverter using complementary TFETs. When a low voltage is applied to the input, the N-TFET is expected to be off and the output voltage will be equal to VDD, but due to the ambipolar conduction of the N-TFET, the output voltage will be less than VDD, for high V<sub>IN</sub>, the ambipolar conduction of P-TFET switches on and so output voltage cannot reach OV [21-22]. And this means that ambipolar conduction leads to incorrect operation of logic gates. In order to reduce the ambipolar conduction, some ways have been proposed, such as: spacer and contact engineering [23-24], non-uniform drain doping [25], using dual material gate dielectric [26], overlapping of the gate on the drain region [27-28]. Also, the tapered channel structure with a higher thickness at the source side, has reduced the ambipolar conduction [29].

In the present work, we show in several structures how the combination of dual material gate with drain gate overlap and source pocket insertion can reduce the ambipolar current and increase the ON-state current of a conventional DG-TFET. Also, by calculating  $I_{ON}/I_{OFF}$  ratio, transconductance (g<sub>m</sub>), gate-drain capacitance  $(C_{gd})$ , gate-source capacitance  $(C_{gs})$ , and cut-off frequency, we show that the proposed structure increases the device figures of merit for digital and high frequency applications. This paper is organized as follows: In first section, the device structures and simulation models are presented. In the next section, the electrical characteristics of the studied device structures are discussed. And then, the effect of different parameters on the proposed structure operation is investigated. Finally, a summary of the results of this article is presented.

# DEVICES STRUCTURES AND SIMULATION PARAMETERS

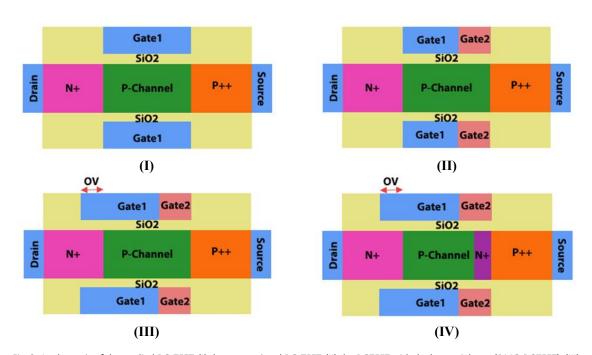

The four different structures of double gate Tunnel-FET (DG-TFET) under study, are shown in Fig. 1. The first structure (I), is a conventional DG-TFET. In the second structure (II), both upper and lower gate metal are engineered with dual material (DMG-DGTFET). That gate work function near the drain side (auxiliary gate) is lower than gate work function near the source side. In third structure (III) the dual material gate combined with gatedrain overlap (GDO-DMG-DGTFET). So that the length of the auxiliary gate has been overlapped on drain by 42nm. The fourth structure (IV), which is the proposed structure, is similar to the third structure, with the difference that the n+ Source Pocket has been added in the fourth structure (SP-GDO-DMG-DGTFET).

The simulation parameters of the structures are presented in Table 1. In this work the simulations are obtained using TCAD SILVACO. There are different tunneling models available in TCAD tools. The choice of tunneling model plays the most important role in the accuracy of the results obtained from the TFET simulation. We have used the non-local tunneling model which can

accurately represent the tunneling physics. In non-local tunneling models, the possible tunneling paths are identified by the simulator and the tunneling probabilities, For the given tunneling path and the given profile of the energy bands are computed by employing techniques like Wentzel-Kramer-Brillouin (WKB) approximation or more rigorous quantum treatment. Also, we have used

the band gap narrowing (BGN) model to calculate heavily doped regions in the devices. In order to consider the rate of generation/recombination we have used Shockley-Read-Hall (SRH) and Auger models. We have also used drift diffusion carrier transport model and Fermi Dirac distribution function model. The model has been calibrated using the data of the silicon DG-TFET of the Ref

Fig. 1. the inverter using complementary TFETs, that ambipolar conduction in TFET leads to incorrect operation of inverter.

Fig. 2. A schematic of the studied DG-TFET. (I) the conventional DG-TFET, (II) the DGTFET with dual material gate (DMG-DGTFET), (III) the DGTFET with combination of dual material gate and gate-drain overlap (GDO-DMG-DGTFET), (IV) the DGTFET with combination of dual material gate and gate-drain overlap and source pocket (SP- GDO-DMG-DGTFET).

[30] and based on the effective mass.

# **RESULTS AND DISCUSSION**

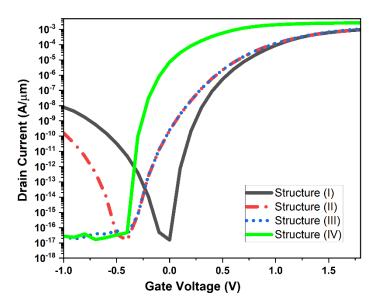

Fig. 3 shows the transfer characteristic of five structures at  $V_{\rm DS}$ = 1V. Conventional TFET has

the highest ambipolar conduction compared to other studied structures. In the second structure, using two gate materials and insertion a material with a lower work function on the drain side has reduced the ambipolar conduction to 1E-1o. In

Fig. 3. The transfer characteristic of five structures at VDS=1.0 V.

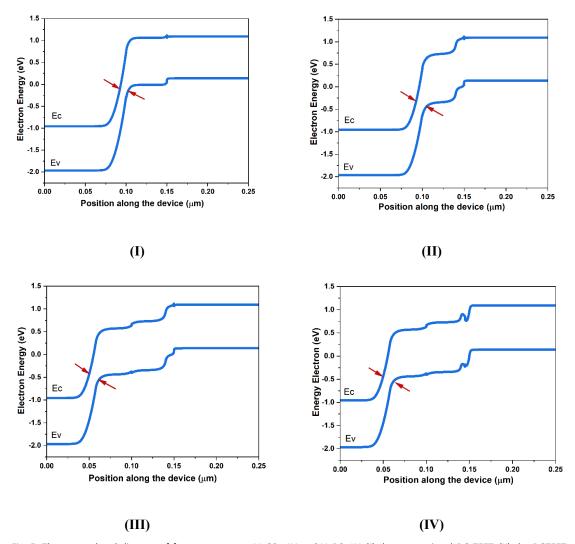

Fig. 4. The energy band diagram of four structures at V\_GS=1V and V\_DS=1V.

the third structure, the simultaneous use of two gate materials with the gate-drain overlap, has led to a significant decrease in ambipolar conduction to 5E-17. In the fourth structure, adding the source pocket has increased the ON-state current. Meanwhile, the ambipolar conduction in this structure is maintained at 5E-17. Consequently, for the case of SP-GDO-DMDG-TFET, both  $\rm I_{ON}$ (enhanced) and the  $I_{amb}$  (reduced) have been improved.

In order to analyze the behavior of the transfer characteristics, the energy band diagram of the structures has been extracted in Fig. 4 and Fig. 5. According to the Wentzel-Kramer-Brillouin (WKB) approximation, the tunneling probability T(E) is calculated using [31]:

$$T(E) = \exp\left(-2\int_{x_{\text{start}}}^{x_{\text{end}}} k(x) \, dx\right) \tag{1}$$

Fig. 5. The energy band diagram of four structures at V\_GS=-1V and V\_DS=1V. (I) the conventional DG-TFET, (II) the DGTFET with dual material gate, (III) the DGTFET with combination of dual material gate and gate-drain overlap, (IV) the DGTFET with combination of dual material gate and gate-drain overlap and source pocket.

where k is the wave vector and  $\mathbf{x}_{\text{start}}$  and  $\mathbf{x}_{\text{end}}$  points are the start and end points of the tunneling path. This equation shows that for a narrower tunneling path, the tunneling probability increases.

Fig. 4 depicts the energy band diagram of four structures at  $V_{GS}$  =1V and  $V_{DS}$  =1V. In the fourth structure, the tunneling width at the source-channel junction, is less compared to the other three structures, so according to the above theorem, the tunneling probability is higher than other structures and as a result, it has a

highest ON-state current. In other structures, the tunneling width appears to be the same and thus have the same  $I_{ON}$ .

Fig. 5 shows the energy band diagram of four structures at  $V_{GS}$  = -1V and  $V_{DS}$  =1V. In the n-type TFET device, if the gate voltage is sufficiently negative, ambipolar conduction is created, so that in negative gate voltages the edge of the channel valence band is placed above the edge of the drain conduction band, and the narrowing of the tunneling barrier at the channel-drain junction enables the tunneling from channel to drain. In

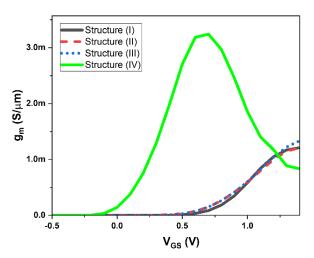

Fig. 6. The transconductance of four structures.

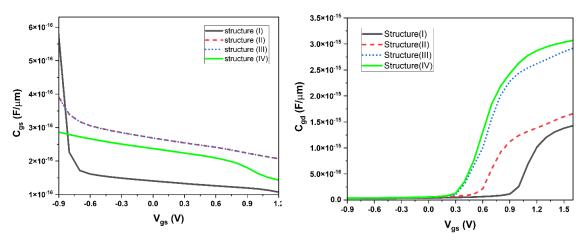

Fig. 7. The Parasitic capacitances. (a) gate-source capacitance, (b) gate-drain capacitance.

Fig. 5, the tunneling barrier width at channel-drain junction, is specified. It can be seen that in the first structure, the tunneling barrier width is less than other structures. And therefore, structure (I) has the highest tunneling probability and highest ambipolar conduction. In the second structure, the tunneling barrier width has decreased compared to structure (I), so the ambipolar conduction is reduced in the second structure. The third and fourth structures have the lowest tunneling barrier width and therefore have the lowest ambipolar conduction.

In TFETs, the gate voltage controls the current, and therefore, the  $I_{\rm DS}/V_{\rm GS}$  ratio at constant drain bias, defined as transconductance, becomes an important parameter for TFETs [32]. To obtain high gain or high driving capability,  $g_{\rm m}$  should be high. The transconductance of All the device structures investigated are shown in Fig. 6. A significant improvement in gm is achieved by adding source pocket in the SP-GDO-DMDG-TFET as shown in Fig. 6.

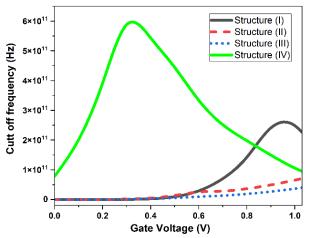

In order to analyze the high frequency performance, the cutoff frequency of all structures

Fig. 8. The cutoff frequency of four structures.

Fig. 9. the  $\rm I_{ON}/I_{OFF}$  ratio and ambipolar conduction of all the devices under investigation.

is studied. Cutoff frequency is defined as the frequency at which the short circuit current gain drops to 0 dB, and it is expressed as [33]:

$$f_T = \frac{g_m}{2\pi(C_{gs} + C_{gd})} \tag{2}$$

where  $g_m$  is the transconductance,  $C_{gs}$  and  $C_{gd}$  are gate-source and gate-drain capacitances. As can be seen from the equation, the cutoff frequency depends directly on  $g_m$  and inversely on

the parasitic capacitances. Parasitic capacitances reduce the cutoff frequency and limit the switching speed. In this work, dual metal gate and gate-drain overlap techniques were used to reduce the ambipolar conduction of TFET, and therefore it is necessary to investigate the effect of dual metal gate and gate-drain overlap and source pocket engineering on parasitic capacitances. The parasitic capacitances of structures including gate-source capacitance and gate-drain capacitance are shown in Fig. 7.

It is evident from Fig. 7 that dual material gate

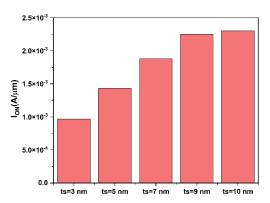

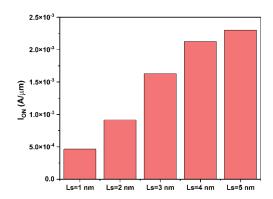

Fig. 10. the effect of source pocket parameters. (a) the thickness of source pocket, (b) the length of source pocket.

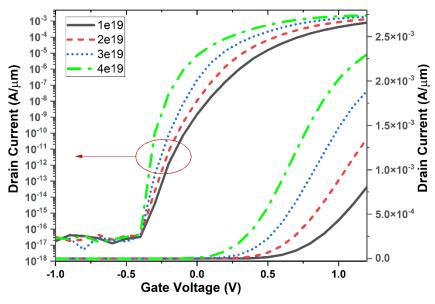

Fig. 11. the effect of source pocket concentration on structure (IV).

and gate-drain overlap techniques has made the parasitic capacitances worse than the conventional TFET.

In order to overcome the degradation in the cutoff frequency caused by dual metal gate and gate-drain overlap, we have added the source pocket to the structure. Adding the source pocket in the proposed structure has led to increase  $g_m$  and has overcome the effect of increasing parasitic capacitances. In Fig. 8, the cutoff frequency of the structures is calculated, as it is evident the overcoming gm has resulted a Preeminent cutoff frequency for the SP-GDO-DMDG-TFET. So that by adding the SP technique, the  $f_{\scriptscriptstyle T}$  peak value has increased from 250 GHz in the conventional DGTFET to 600 GHz.

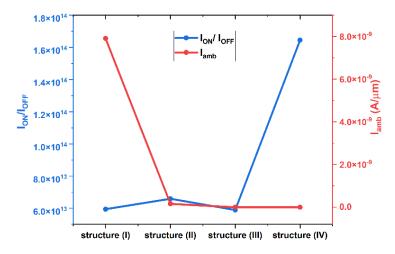

Fig. 9 depicts the  $I_{ON}/I_{OFF}$  ratio and ambipolar conduction of all the devices under investigation. The excellent  $I_{ON}/I_{OFF}$  ratio (1E14) and suppressed ambipolar (5E-17) conduction make the SP-GDO-DMG DGTFET an supreme device for digital applications.

The effect of thickness, length and doping value of source pocket on the performance of structure (IV) is investigated. Fig. 4 shows the effect of changing the length and thickness of the source pocket on the ON-state current. As we can see, the  $I_{\text{ON}}$  increases with the increase of length and thickness of source pocket.

Fig. 11 shows the effect of the source pocket doping concentration on the structure (IV). It can be seen that increasing of the source pocket doping concentration, clearly increases the ON-state current.

## CONCLUSION

In this paper, a structure of DG-TFET was proposed which improves the electrical characteristics of conventional DGTET. We have shown that the integration of dual material gate with gate-drain overlap can significantly reduce the ambipolar conduction. And adding the source pocket to the proposed structure, increases ONstate current. So that the proposed structure has a high I<sub>ON</sub>/I<sub>OFF</sub> ratio (1E14) and the lowest ambipolar conduction (5E-17). We showed that the gatedrain overlap worsens the effect of parasitic capacitances, but in the proposed structure, adding the source pocket leads to high gm in the proposed structure, which dominates the effect of parasitic capacitances. So that the proposed structure has a high cut off frequency (600GHz)

and is very suitable for high frequency applications.

#### **CONFLICT OF INTEREST**

The authors declare that there is no conflict of interests regarding the publication of this manuscript.

#### **REFERENCES**

- Taur Y, Ning TH. Fundamentals of Modern VLSI Devices: Cambridge University Press; 2021 2021/12/02.

- Knoch J, Appenzeller J. A novel concept for field-effect transistors - the tunneling carbon nanotube FET. 63rd Device Research Conference Digest, 2005. DRC '05.: IEEE; 2005. p. 153-156.

- Mukundrajan R, Cotter M, Saripalli V, Irwin MJ, Datta S, Narayanan V. Ultra Low Power Circuit Design Using Tunnel FETs. 2012 IEEE Computer Society Annual Symposium on VLSI; 2012/08: IEEE; 2012. p. 153-158.

- Park B-G. Tunneling Field-Effect Transistors for Ultra-Low-Power Application. KAIST Research Series: Springer Netherlands; 2015. p. 3-31.

- Ionescu AM, Riel H. Tunnel field-effect transistors as energyefficient electronic switches. Nature. 2011;479(7373):329-337

- Knoch J, Mantl S, Appenzeller J. Impact of the dimensionality on the performance of tunneling FETs: Bulk versus onedimensional devices. Solid-State Electron. 2007;51(4):572-578.

- Lin Z, Chen P, Ye L, Yan X, Dong L, Zhang S, et al. Challenges and Solutions of the TFET Circuit Design. IEEE Transactions on Circuits and Systems I: Regular Papers. 2020;67(12):4918-4931.

- Pal A, Sachid AB, Gossner H, Rao VR. Insights Into the Design and Optimization of Tunnel-FET Devices and Circuits. IEEE Trans Electron Devices. 2011;58(4):1045-1053.

- Gopi C, Chauhan SS. Double-gate Ge, In As-based tunnel FETs with enhanced ON-current. 2016 International Conference on Communication and Signal Processing (ICCSP); 2016/04: IEEE; 2016. p. 0639-0641.

- Lu Y, Zhou G, Li R, Liu Q, Zhang Q, Vasen T, et al. Performance of AlGaSb/InAs TFETs With Gate Electric Field and Tunneling Direction Aligned. IEEE Electron Device Lett. 2012;33(5):655-657.

- 11. Rajamohanan B, Mohata D, Ali A, Datta S. Insight into the output characteristics of III-V tunneling field effect transistors. Appl Phys Lett. 2013;102(9):092105.

- Yu Z, Dong Y, Lin X, Zhang L. Current enhanced double-gate TFET with source pocket and asymmetric gate oxide. 2016 IEEE International Nanoelectronics Conference (INEC); 2016/05: IEEE; 2016. p. 1-2.

- 13. Boucart K, Ionescu AM. Double-Gate Tunnel FET With High- Gate Dielectric. IEEE Trans Electron Devices. 2007;54(7):1725-1733.

- 14. Lin H-H, Hu VP-H. Device design of vertical nanowire III-V heterojunction TFETs for performance enhancement. 2018 7th International Symposium on Next Generation Electronics (ISNE); 2018/05: IEEE; 2018. p. 1-4.

- Jiang Z, Zhuang Y, Li C, Wang P, Liu Y. Drive Current Enhancement in TFET by Dual Source Region. Journal of Electrical and Computer Engineering. 2015;2015:1-11.

- 16. Toh E-H, Wang GH, Samudra G, Yeo Y-C. Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high

J Nanostruct 15(3): 1406-1415, Summer 2025

- performance applications. J Appl Phys. 2008;103(10).

- 17. Loh W-Y, Jeon K, Kang CY, Oh J, Patel P, Smith C, et al. Sub-60nm Si tunnel field effect transistors with I<sub>ON</sub>>100 μA/ μm. 2010 Proceedings of the European Solid State Device Research Conference; 2010/09: IEEE; 2010. p. 162-165.

- Toh E-H, Wang GH, Samudra G, Yeo Y-C. Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl Phys Lett. 2007;90(26).

- Kumar S, Khanna G. ON current improvement techniques for double gate-tunnel field effect transistor. 2017 4th International Conference on Signal Processing, Computing and Control (ISPCC); 2017/09: IEEE; 2017. p. 391-395.

- Saurabh S, Kumar MJ. Fundamentals of Tunnel Field-Effect Transistors: CRC Press; 2016 2016/10/26.

- Paul DJ, Khosru QDM. Improved bilayer phosphorene TFET inverter performance by reduction of ambipolarity. AIP Advances. 2018;8(7).

- 22. Spano CE, Mo F, Claudino RA, Ardesi Y, Ruo Roch M, Piccinini G, et al. Tunnel Field-Effect Transistor: Impact of the Asymmetric and Symmetric Ambipolarity on Fault and Performance in Digital Circuits. Journal of Low Power Electronics and Applications. 2022;12(4):58.

- 23. Hraziia, Vladimirescu A, Amara A, Anghel C. An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid-State Electron. 2012;70:67-72.

- 24. Anghel C, Hraziia, Gupta A, Amara A, Vladimirescu A. 30-nm Tunnel FET With Improved Performance and Reduced Ambipolar Current. IEEE Trans Electron Devices. 2011;58(6):1649-1654.

- 25. Vijayvargiya V, Vishvakarma SK. Effect of Drain Doping

- Profile on Double-Gate Tunnel Field-Effect Transistor and its Influence on Device RF Performance. IEEE Transactions on Nanotechnology. 2014;13(5):974-981.

- 26. Choi WY, Lee W. Hetero-Gate-Dielectric Tunneling Field-Effect Transistors. IEEE Trans Electron Devices. 2010;57(9):2317-2319.

- Abdi DB, Jagadesh Kumar M. Controlling Ambipolar Current in Tunneling FETs Using Overlapping Gate-on-Drain. IEEE Journal of the Electron Devices Society. 2014;2(6):187-190.

- Shaker A, Ossaimee M, Zekry A, Abouelatta M. Influence of gate overlap engineering on ambipolar and high frequency characteristics of tunnel-CNTFET. Superlattices Microstruct. 2015;86:518-530.

- Morgan Y, Abouelatta M, El-Banna M, Shaker A. Tapered-Shape Channel Engineering for Suppression of Ambipolar Current in TFET. 2020 IEEE 5th International Conference on Integrated Circuits and Microsystems (ICICM); 2020/10/23: IEEE; 2020. p. 197-200.

- Karbalaei M, Dideban D, Heidari H. A simulation study of the influence of a high-k insulator and source stack on the performance of a double-gate tunnel FET. Journal of Computational Electronics. 2020;19(3):1077-1084.

- 31. Vender J, Suchan T. QSR NUD\*IST and ATLAS/ti. Cartographic Perspectives. 1998(31):37-40.

- Madan J, Chaujar R. Gate drain-overlapped-asymmetric gate dielectric-GAA-TFET: a solution for suppressed ambipolarity and enhanced ON state behavior. Appl Phys A. 2016;122(11).

- 33. Dash S, Sahoo GS, Mishra GP. Improved Cut-off Frequency for Cylindrical Gate TFET Using Source Delta Doping. Procedia Technology. 2016;25:450-455.

J Nanostruct 15(3): 1406-1415, Summer 2025